# SmartMC <sup>™</sup> II Modem Codec

Host-Processed, V.90/K56flex<sup>TM</sup> Modem Codec (MC) Device Set with Host Side Device (11246) and SmartDAA<sup>TM</sup> (20463) for AC-link (AC'97 2.1) Applications

The Conexant<sup>™</sup> SmartMC II V.90/K56flex<sup>™</sup> Modem Codec (MC) Device Set with SmartDAA technology supports analog data up to 56 kbps, analog fax to 14.4 kbps, voice/telephone answering machine (TAM), and AC-link (AC'97) interface operation. The modem operates with PSTN telephone lines in the U.S. and world-wide. Table 1 lists the available models.

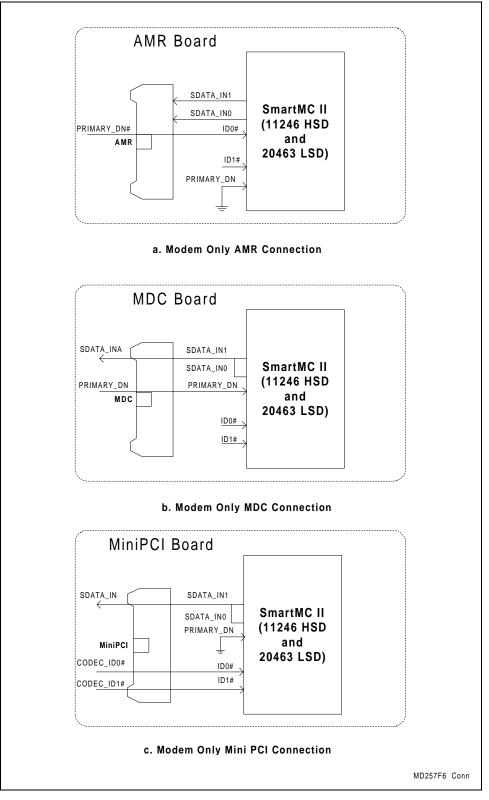

The SmartMC II<sup>™</sup> MC with AC-link interface supports Audio/Modem Riser (AMR), Mobile Daughter Card (MDC), and Mini PCI interfaces for applications such as embedded/plug-in modems.

Conexant's SmartDAA technology (patent pending) eliminates the need for a costly line transformer, relays, and opto-isolators typically used in discrete DAA (Data Access Arrangement) implementations. The SmartDAA architecture also simplifies product implementation by eliminating the need for country-specific board configurations enabling world-wide homologation of a single modem board design.

The SmartDAA system side powered DAA operates reliably without drawing power from the line, unlike line-powered DAAs which operate poorly when line current is insufficient due to long lines or poor line conditions. Enhanced features, such as monitoring of local extension status without going off-hook, are also supported.

Incorporating Conexant's proprietary Digital Isolation Barrier (DIB) design (patent pending) and other innovative DAA features, the SmartDAA architecture simplifies application design, minimizes layout area, and reduces component cost for world-wide support.

For over a decade, Conexant has assisted customers with DAA technology and homologation. This expertise and system level approach has been leveraged in this product.

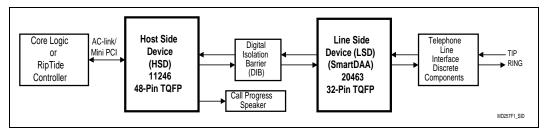

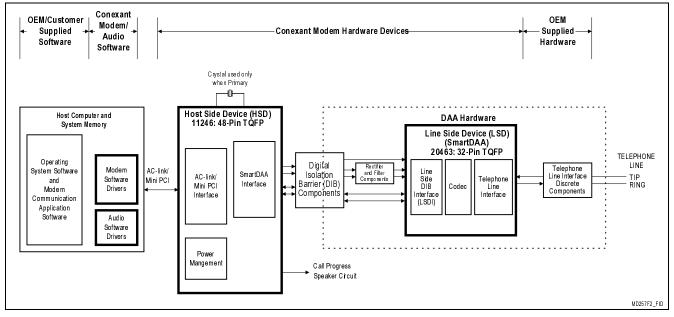

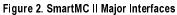

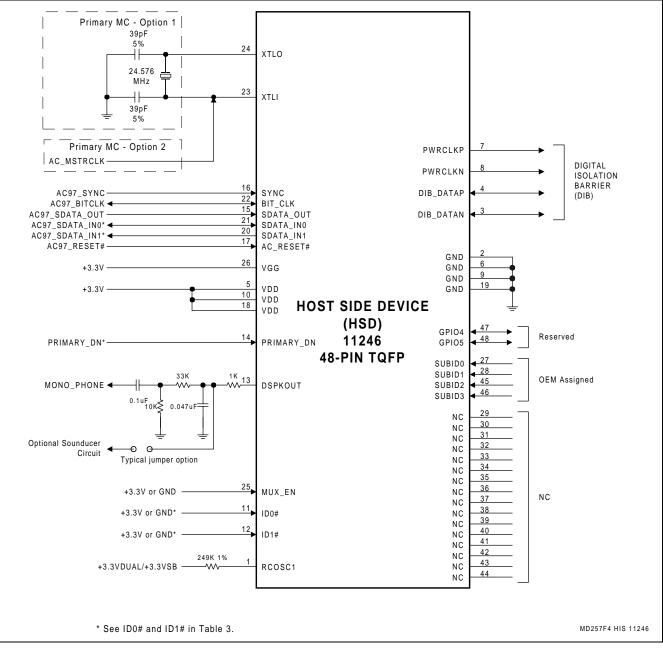

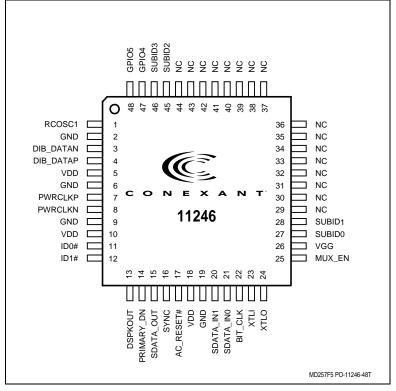

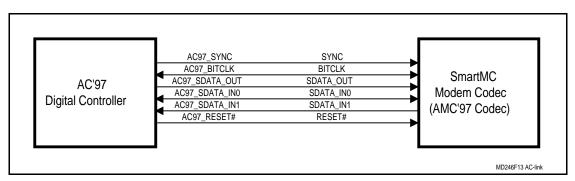

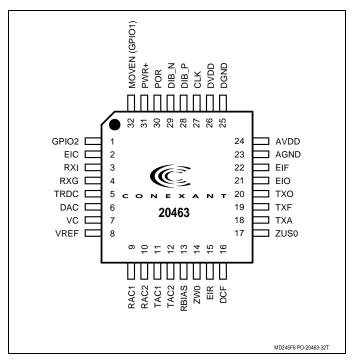

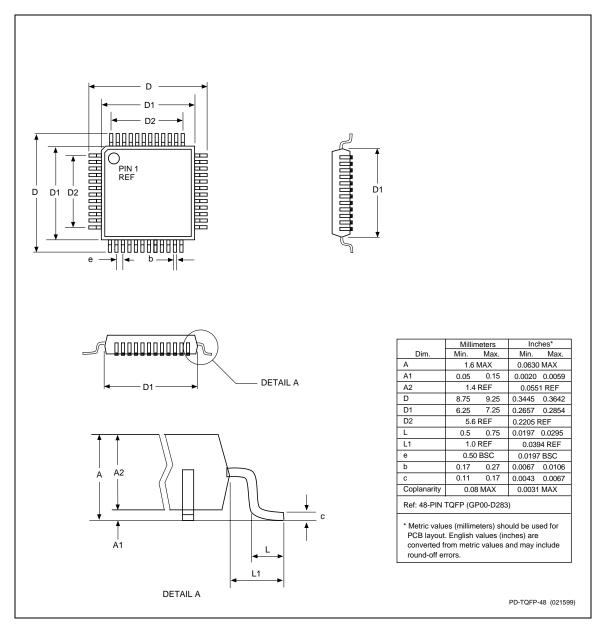

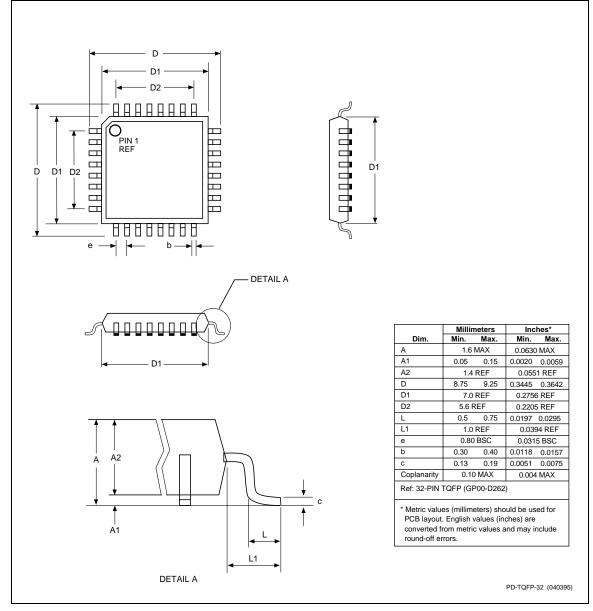

The SmartMC II device set, consisting of an 11246 Host Side Device (HSD) in a 48-pin TQFP and a 20463 Line Side Device (LSD) (SmartDAA device) in a 32-pin TQFP, supports data/fax/voice/TAM and DAA (Digital Access Arrangement)/telephone line interface functions (Figure 1). Figure 2 identifies the major hardware signal interfaces. Figure 3 identifies typical supported MC configurations.

Audio recording and playback over the telephone line interface using A-Law,  $\mu$ -Law, or linear coding at 8 kHz sample rate supports applications such as remote digital telephone answering machine (TAM).

## **Distinguishing Features**

- V.90 data/V.17 fax soft modem, MMX optimized

- SmartDAA technology

- Eliminates many costly traditional DAA discrete components

- Reduces modem and DAA board footprint

- Allows a single modem board design to be approved for world-wide shipments

- Line-in-use detection

- Remote hangup detection

- Extension off-hook detection

- Wake-up on ring for primary/secondary codec

- Telephony/voice/TAM

- Supports Conexant RipTide D7400/D7300 controllers and selected AC'97-compliant core logic

- Supports soft speakerphone using WDM drivers

- Data/Fax/Voice call discrimination

- World-class operation (optional)

- Industry standard communication commands

- AC-link (AC'97 2.1 compatible) host interface

- Single line Data/Fax/Voice/TAM modem codec

- Operable as a primary or a secondary codec

- Supports AMR, MDC, and Mini PCI host interface

- Sleep current less than 1 mA

- System compatibilities

- Windows Driver Model (WDM)

- Windows 95/98, Windows NT 4.0, Windows 2000

- Microsoft PC 98 and PC 99 compliant

- Advanced Power Management (APM and ACPI)

- V.80 synchronous access

- +3.3V operation with +5V tolerant digital inputs

## Applications

- Primary or secondary modem AMR and MDC card

- Speakerphone using Conexant audio products

- Embedded/plug-in Mini PCI modems

Figure 1. SmartMC II Devices and Major Signal Interfaces

|                                | Model/Order/Pa                                                                     | Supported Functions                                    |                                                                      |                                 |                                                                          |            |

|--------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------|------------|

| Marketing No.*                 | Device Set Order<br>No.                                                            | Host Side Device<br>(HSD)<br>[48-Pin TQFP]<br>Part No. | Line Side Device<br>(LSD)<br>(SmartDAA)<br>[32-Pin TQFP]<br>Part No. | Ultra-Low<br>Power<br>Operation | V.90/K56flex Data,<br>V.17 Fax,<br>Voice/TAM,<br>Basic Audio<br>Software | World-wide |

| SmartMC II/L                   | DSAC-L200-001                                                                      | 11246-12                                               | 20463-12                                                             | Y                               | Y                                                                        | —          |

| SmartMC II/WL                  | DSAC-L300-201                                                                      | 11246-12                                               | 20463-11                                                             | Y                               | Y                                                                        | Y          |

| L<br>2. Supported functions (N | World-wide<br>Ultra low power<br>( = Supported; – = Not s<br>ephone answering macl |                                                        | nd record through telep                                              | hone line)                      |                                                                          |            |

#### Table 1. SmartMC || Models and Functions

Information provided by Conexant Systems, Inc. is believed to be accurate and reliable. However, no responsibility is assumed by Conexant for its use, nor any infringement of patents, copyrights, or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights or copyright of Conexant other than for circuitry embodied in Conexant products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without notice.

Conexant products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Conexant product can reasonably be expected to result in personal injury or death. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

K56flex is a trademark of Conexant Systems, Inc. and Lucent Technologies. Conexant, the Conexant C symbol, "What's Next in Communications Technologies", SmartDAA, SmartMC, and RipTide are trademarks of Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of third parties [their respective companies]. All other marks mentioned herein are the property of their respective [holders] owners.

Figure 3. Typical Supported MC Configurations

# **Detailed Features**

## **General Modem Features**

- V.90 data modem with receive rates up to 56 kbps and send rates up to V.34 rates

- ITU-T V.90, K56flex, V.34 (33.6 kbps), V.32 bis, V.32, V.22 bis, V.22, V.23, and V.21; Bell 212A and 103

- V.42 LAPM and MNP 2-4 error correction

- V.42 bis and MNP 5 data compression

- V.250 (ex V.25 ter) and V.251 (ex V.25 ter Annex A) commands

- V.17 fax modem with send and receive rates up to 14.4 kbps

- V.17, V.29, V.27 ter, and V.21 ch 2

- EIA/TIA 578 Class 1 and T.31 Class 1.0 commands

- Telephony/Voice/TAM

- V.253 commands

- 8-bit μ-Law/A-Law coding (G.711)

- 8-bit/16-bit linear coding

- 8 kHz sample rate

- Concurrent DTMF detect, ring detect and caller ID

- V.80 synchronous access mode supports host-controlled communication protocols with H.324 interface support

- V.8/V.8bis and V.251 (ex V.25 ter Annex A) commands

- Data/Fax/Voice call discrimination

- Host software-based signal processing

- Single configuration profile stored in host

- World-Class (W model)

- Complies to TBR21 and other country requirements

Caller ID detection

- System compatibilities

- Windows Driver Model (WDM)

- Windows 95/98 operating system

- Windows NT 4.0, Windows 2000 operating systems

- Microsoft PC 98 and PC 99 Design Initiative compliant

- Advanced Power Management (APM and ACPI)

- Unimodem/V compliant

- Pentium 166 MMX MHz-compatible or greater

- 32 Mbyte RAM or more

- Thin packages support low profile designs

- (1.6 mm max. height)

- HSD (11246): 48-pin TQFP

- LSD (20463): 32-pin TQFP

- +3.3V operation with +5V tolerant digital inputs

## AC-link (AC'97) Host Interface Features

- Operates as a single-line Data/Fax/Voice/TAM modem

- AC'97 rev 2.1 compatible codec with the LSD and DIB (uses protocol slot 5 and 12)

- Uses +3.3VSB for power management mode

- Wake-on-ring in primary and secondary codec

- Sleep current: 1 mA typical

- Supports Conexant RipTide D7400/D7300 controllers and selected AC'97-compliant core logic

- Supports soft speakerphone using WDM drivers

- Operable as either a primary or a secondary codec selected by external pin configuration.

- BIT\_CLK is the input bit clock input in secondary codec operation

- BIT\_CLK is the output bit clock (derived from external crystal) in primary codec operation

- Supports Power Management

- ACPI Power Management Registers

- APM support

- Wake-on ring in D3cold

### SmartDAA Features

- System side powered DAA operates under poor line current supply conditions

- Wake-on-ring

- Ring detection

- Line polarity reversal detection

- Line current loss detection

- Pulse dialing

- Line-in-use detection detects even while on-hook

- Remote hang-up detect for efficient call termination

- Extension pickup detect

- Handset exclusion (patent pending)

- Call waiting detection

- Digital PBX line protection

- Meets world-wide DC VI Masks requirements (W model)

## Description

## General

Modem operation, including dialing, call progress, telephone line interface, and host interface functions are supported and controlled through the V.250, V.251, and V.253-compatible command set.

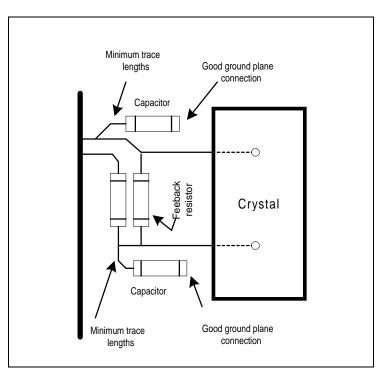

The modem hardware connects to the host processor via an AC-link interface. The OEM adds a 24.576 MHz crystal circuit if Primary MC operation is required, optional digital speaker circuit, DIB components, LSD power rectifier and filter components, telephone line interface components, control straps, and other supporting discrete components as required and supported by the model to complete the system.

## Host Modem Software

The host modem software performs the following tasks:

- General modem control, which includes command sets, fax Class 1, voice/TAM, speakerphone through Conexant WDM driver or RipTide configuration, error correction, data compression, and operating system interface functions.

- 2. Modem data pump signal processing, which includes data and facsimile modulation and demodulation, as well as voice/TAM sample formatting.

- 3. SmartDAA control, which includes HSD SmartDAA Interface control, LSD configuration and control, telephone interface parameter control, and telephone line impedance control.

Configurations of the modem software are provided to support modem models listed in Table 1.

#### Data/Fax Modes

As a V.90/K56flex data modem, the modem can receive data from a digitally connected central site modem (CSM) at line speeds up to 56 kbps. Asymmetrical data transmission supports sending data up to V.34 rates. This mode can fallback to full-duplex V.34 mode, and to lower rates as dictated by line conditions.

As a V.34 data modem, the modem can operate in 2-wire, full-duplex, asynchronous modes at line rates up to 33.6 kbps. Data modem modes perform complete handshake and data rate negotiations. Using V.34 modulation to optimize modem configuration for line conditions, the modem can connect at the highest data rate that the channel can support from 33600 bps down to 2400 bps with automatic fallback. Automode operation in V.34 is provided in accordance with PN3320 and in V.32 bis in accordance with PN2330. All tone and pattern detection functions required by the applicable ITU or Bell standard are supported.

In fax modem mode, the modem can operate in 2-wire, half-duplex, synchronous modes and can support Group 3 facsimile send and receive speeds of 14400, 12000, 9600, 7200, 4800, and 2400 bps. Fax data transmission and reception performed by the modem are controlled and monitored through the fax EIA/TIA-578 Class 1 and T.31 Class 1.0 command interface. Full HDLC formatting, zero insertion/deletion, and CRC generation/checking are provided.

#### Synchronous Access Mode (SAM) - Video Conferencing

V.80 synchronous access mode between the modem and the host/DTE is provided for host-controlled communication protocols, e.g., H.324 video conferencing applications.

Voice-call-first (VCF) before switching to a videophone call is also supported.

#### Voice/TAM Mode

Voice/TAM Mode features include 8-bit  $\mu$ -Law, A-Law, and linear coding at 8 kHz sample rates. Tone detection/generation, call discrimination, and concurrent DTMF detection are also supported. ADPCM (4-bit IMA) coding is also supported to meet Microsoft WHQL logo requirements.

Voice/TAM Mode is supported by three submodes:

- 1. Online Voice Command Mode supports connection to the telephone line or, for speakerphone configuration, to a microphone/speaker.

- 2. Voice Receive Mode supports recording voice or audio data input from the telephone line or, for speakerphone configuration, from a microphone.

- 3. Voice Transmit Mode supports playback of voice or audio data to the telephone line or, for speakerphone configuration, to a speaker.

- 4. Full-duplex voice supports concurrent voice receive and transmit.

#### **Reference Design**

An AMR data/fax/voice/TAM/handset exclusion reference design card and an MDC data/fax/voice/TAM reference design card are available to minimize application design time and costs.

The card is pretested to pass FCC Part 15, Part 68, and TBR 21.

A design package is available in electronic form. The design package includes schematics, bill of materials (BOM), vendor parts list (VPL), board layout files in Gerber format, and complete documentation.

The reference designs are production ready for immediate manufacturing. The design can also be used for the basis of a custom design by the OEM to accelerate design completion for rapid market entry.

## **Hardware Description**

SmartDAA<sup>™</sup> technology (patent pending) eliminates the need for a costly analog transformer, relays, and optoisolators that are typically used in discrete DAA implementations. The programmable SmartDAA architecture simplifies product implementation in worldwide markets by eliminating the need for country-specific components.

#### Host Side Device (HSD)

The HSD serves as an AC'97 2.1 -compatible modem codec (MC) packaged in a 48-pin TQFP. It can function as a primary or secondary AC-link codec as selected by the ID0#, ID1#, and PRIMARY\_DN pins. As a primary codec, it uses an attached 24.576 MHz crystal to generate internal clocks and produce the 12.288 MHz AC-link bit clock (BIT\_CLK). As a secondary codec, it uses an incoming 12.288 MHz BIT\_CLK signal to generate its internal clocks.

Internal functions include an AC-link (AC'97) Interface, Power Management Interface, Caller ID Detection, and a SmartDAA Interface.

The AC-link Interface connects directly to core logic or a PCI-based controller, typically through an AMR, MDC, or Mini PCI connector.

The SmartDAA Interface communicates with, and supplies power and clock to, the LSD through the DIB.

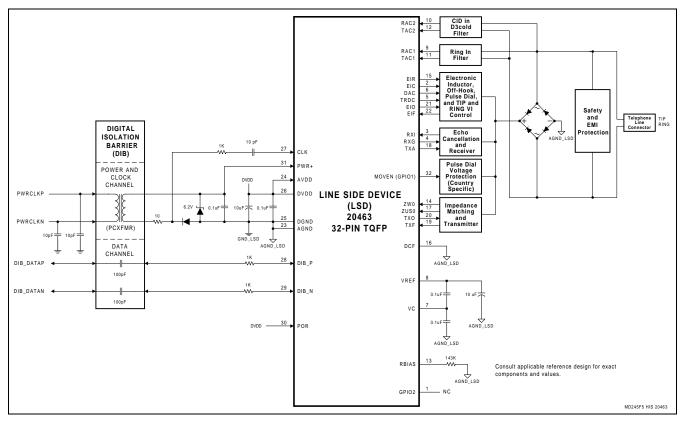

## Digital Isolation Barrier (DIB) (OEM Supplied)

The DIB electrically DC isolates the HSD from the LSD and telephone line. The HSD is connected to a fixed digital ground and operates with standard CMOS logic levels. The LSD is connected to a floating ground and can tolerate high voltage input (compatible with telephone line and typical surge requirements).

The DIB power and clock transformer (PCXFMR) couples power and clock from the HSD to the LSD.

The DIB data channel supports bidirectional serial transfer of data, control, and status information between the HSD and the LSD.

### Line Side Device (LSD)

The LSD includes a Line Side DIB Interface (LSDI), a coder/decoder (codec), and a Telephone Line Interface (TLI).

The LSDI communicates with, and receives power and clock from, the SmartDAA interface in the HSD through the DIB.

LSD power is received from the DIB PCXFMR secondary winding through a half-wave rectifying diode and capacitive power filter circuit. The CLK input is also accepted from the PCXFMR secondary winding through a capacitor and a resistor in series. The LSD DGND is referenced to the bottom of the PCXFMR secondary winding.

Information is transferred between the LSD and the HSD through the DIB\_P and DIB\_N pins. These pins connect to the HSD DIB\_DATAP and DIB\_DATAN pins, respectively, through the DIB.

The TLI integrates DAA and direct telephone line interface functions and connects directly to the line TIP and RING pins, as well as to external line protection components.

Direct LSD connection to TIP and RING allows real-time measurement of telephone line parameters, such as the telephone central office (CO) battery voltage, individual telephone line (copper wire) resistance, and allows dynamic regulation of the off-hook TIP and RING voltage and total current drawn from the central office (CO). This allows the modem to maintain compliance with U.S. and world-wide regulations and to actively control the DAA power dissipation.

## HSD (11246) Hardware Pins and Signals

#### General

#### AC-link Host Interface

The AC-link host interface conforms to AC'97 rev 2.1 compatible for a single line Data/Fax/Voice/TAM only modem codec.

The supported AC-link signals are:

- Bit Clock (BIT\_CLK), input/output

- Frame Sync (SYNC), input

- Serial Data Output (SDATA\_OUT), input

- Serial Data Input 0 (SDATA\_IN0), input/output

- Serial Data Input 1 (SDATA\_IN1), output

- AC '97 Master Hardware Reset (AC\_RESET#), input

#### **Control Signals**

Control signals from straps or the host are:

- Primary Down (PRIMARY\_DN), input

- Mux Enable (MUX\_EN), input

- Codec ID (ID0# and ID1#); input

- Sub Assembly ID (SUBID[3:0]); input

#### LSD Interface (Through DIB)

The DIB interface signals are:

- Clock and Power Plus (PWRCLKP); output

- Clock and Power Minus (PWRCLKN); output

- Data Plus (DIB\_DATAP); input/output

- Data Minus (DIB\_DATAN); input/output

#### Digital Speaker Interface

The digital speaker interface signal is:

• Digital speaker output (DSPKOUT); output

DSPKOUT is a square wave output in Data/Fax mode which can be optionally connected to an AC'97 audio device to enable playback of call progress through the analog mixer in the AC'97 device. The DSPKOUT output can be also be connected to a low-cost on-board speaker, e.g., a sounducer, without the use of an external op-amp.

#### Pin Assignments and Signal Definitions

The HSD (11246) 48-pin TQFP hardware interface signals are shown by major interface in Figure 4, are shown by pin number in Figure 5, and are listed by pin number in Table 2.

The HSD (11246) hardware interface signals are defined in Table 3.

The HSD (11246) digital characteristics are defined in Table 4.

Figure 4. HSD (11246) 48-Pin TQFP Hardware Interface Signals

Figure 5. HSD (11246) 48-Pin TQFP Pin Signals

|          |            |                       | Table 2. HSD (11246) 4                                                                                                                 | r       | -                   |          |                   |

|----------|------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------|----------|-------------------|

| Pin      | Signal Lab | el I/O Type           | Interface                                                                                                                              | Pin     | Signal Label        | I/O Type | Interface         |

| 1        | RCOSC1     |                       | +3.3Vdual through 249 KΩ, 1%                                                                                                           | 25      | MUX_EN              | lt       | GND               |

| 2        | GND        | GND                   | GND                                                                                                                                    | 26      | VGG                 | REF      | +3.3V             |

| 3        | DIB_DATAN  | Idd/Odd               | DIB: Data Negative Channel capacitor                                                                                                   | 27      | SUBID0              | lt       | Sub Assembly ID 0 |

| 4        | DIB_DATAP  | Idd/Odd               | DIB: Data Positive Channel capacitor                                                                                                   | 28      | SUBID1              | lt       | Sub Assembly ID 1 |

| 5        | VDD        | PWR                   | +3.3V                                                                                                                                  | 29      | NC                  |          | NC                |

| 6        | GND        | GND                   | GND                                                                                                                                    | 30      | NC                  |          | NC                |

| 7        | PWRCLKP    | Odpc                  | DIB: PCXFMR Primary Top Winding                                                                                                        | 31      | NC                  |          | NC                |

| 8        | PWRCLKN    | Odpc                  | DIB: PCXFMR Primary Bottom<br>Winding                                                                                                  | 32      | NC                  |          | NC                |

| 9        | GND        | GND                   | GND                                                                                                                                    | 33      | NC                  |          | NC                |

| 10       | VDD        | PWR                   | +3.3V                                                                                                                                  | 34      | NC                  |          | NC                |

| 11       | ID0#       | lt                    | See ID0# and ID1# in Table 3                                                                                                           | 35      | NC                  |          | NC                |

| 12       | ID1#       | lt                    | See ID0# and ID1# in Table 3                                                                                                           | 36      | NC                  |          | NC                |

| 13       | DSPKOUT    | Ot2                   | Al: Digital Speaker                                                                                                                    | 37      | NC                  |          | NC                |

| 14       | PRIMARY_D  | N It                  | See ID0# and ID1# in Table 3                                                                                                           | 38      | NC                  |          | NC                |

| 15       | SDATA_OUT  | lac                   | AC-link: AC97_SDATA_OUT                                                                                                                | 39      | NC                  |          | NC                |

| 16       | SYNC       | lac                   | AC-link: AC97_SYNC                                                                                                                     | 40      | NC                  |          | NC                |

| 17       | AC_RESET#  | lac                   | AC-link: AC97_RESET                                                                                                                    | 41      | NC                  |          | NC                |

| 18       | VDD        | PWR                   | +3.3V                                                                                                                                  | 42      | NC                  |          | NC                |

| 19       | GND        | GND                   | GND                                                                                                                                    | 43      | NC                  |          | NC                |

| 20       | SDATA_IN1  | Oac                   | See ID0# and ID1# in Table 3                                                                                                           | 44      | NC                  |          | NC                |

| 21       | SDATA_IN0  | lac/Oac               | See ID0# and ID1# in Table 3                                                                                                           | 45      | SUBID2              | lt       | Sub Assembly ID 2 |

| 22       | BIT_CLK    | lac/Oac               | AC-link: AC97_BITCLK                                                                                                                   | 46      | SUBID3              | lt       | Sub Assembly ID 3 |

| 23       | XTLI       | Ix                    | For Primary MC, 24.576 MHz crystal<br>circuit or clock oscillator circuit<br>(AC_MSTRCLK).<br>For Secondary MC, can be NC.             | 47      | GPIO4               | lt/Ot12  | NC                |

| 24       | XTLO       | Ox                    | For Primary MC, 24.576 MHz crystal<br>circuit, or leave open if XTLI is<br>connected to clock circuit.<br>For Secondary MC, can be NC. | 48      | GPIO5               | lt/Ot12  | NC                |

| 1. I/O 1 | lac I      |                       | nk-compatible, $C_{IN} = 50 \text{ pF}$ (see Table 4)                                                                                  |         |                     |          |                   |

|          | lac/Oac I  | Jigital Input, AC-lir | nk-compatible, C <sub>IN</sub> = 50 pF/Digital output,                                                                                 | AC-IINK | -compatible (see 1a | DIE 4)   |                   |

|          | Idd/Odd [  | DIB data input/DIB    | data output                                                                                                                            |         |                     |          |                   |

|          | lt [       | Digital input, TTL-c  | compatible                                                                                                                             |         |                     |          |                   |

|          | lx (       | Crystal input         |                                                                                                                                        |         |                     |          |                   |

|          | Oac I      | Digital output, AC-   | link-compatible (see Table 4)                                                                                                          |         |                     |          |                   |

|          |            | DIB power and clo     |                                                                                                                                        |         |                     |          |                   |

|          | Ot12 [     | Digital output, TTL   | -compatible, 12 mA, $Z_{INTERNAL} = 32 \Omega$                                                                                         |         |                     |          |                   |

|          |            | Crystal input         | ···· - · · · · · ·                                                                                                                     |         |                     |          |                   |

|          | 0          | Digital Interface Ba  | arrier                                                                                                                                 |         |                     |          |                   |

|          |            | No external conne     |                                                                                                                                        |         |                     |          |                   |

| 1        |            | to external conner    |                                                                                                                                        |         |                     |          |                   |

#### Table 2. HSD (11246) 48-Pin TQFP Pin Signals

## Table 3. HSD (11246) 48-pin TQFP Pin Signal Definitions

| Label  | Pin            | I/O Type | Signal Name/Description                                                                                                                                                                                                                                                                                   |

|--------|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                |          | System                                                                                                                                                                                                                                                                                                    |

| VDD    | 5, 10, 18      | PWR      | Digital Supply Voltage. Connect to +3.3V.                                                                                                                                                                                                                                                                 |

| GND    | 2, 6, 9,<br>19 | GND      | Digital Ground. Connect to digital ground.                                                                                                                                                                                                                                                                |

| XTLI   | 23             | lx       | <b>Crystal In/Clock In.</b> For Primary MC, connect to 24.576 MHz crystal circuit or clock oscillator circuit (AC_MSTRCLK). For Secondary MC, pins can be left open.                                                                                                                                      |

| XTLO   | 24             | Ox       | <b>Crystal Out.</b> For Primary MC, connect to 24.576 MHz crystal circuit, or leave open if XTLI is connected to clock circuit. For Secondary MC, pins can be left open.                                                                                                                                  |

| VGG    | 26             | REF      | Reference Voltage. Connect to +3.3V.                                                                                                                                                                                                                                                                      |

| MUX_EN | 25             | lt       | Mux Enable. Connect to +3.3V (High) or GND (Low).                                                                                                                                                                                                                                                         |

|        |                |          | High defines SDATA_IN0 as an input for use when the SmartMC is a Secondary MC.                                                                                                                                                                                                                            |

|        |                |          | In this case, the Smart MC multiplexes the AC'97 audio input data on SDATA_IN0 with the internal modem data, then outputs the data on SDATA_IN1.                                                                                                                                                          |

| ID0#   | 11             | lt       | Codec ID. Used in conjunction with PRIMARY_DN to select modem codec operation as a                                                                                                                                                                                                                        |

| ID1#   | 12             | lt       | primary or secondary codec, as follows and shown in Figure 6:                                                                                                                                                                                                                                             |

|        |                |          | For a Modem-Only Riser Card:                                                                                                                                                                                                                                                                              |

|        |                |          | 1. Connect PRIMARY_DN to GND.                                                                                                                                                                                                                                                                             |

|        |                |          | 2. Connect SDATA_IN0 to AC-link AC97_SDATA_IN0 through 33 Ω.                                                                                                                                                                                                                                              |

|        |                |          | 3. Connect SDATA_IN1 to AC-link AC97_SDATA_IN1 through 33 Ω.                                                                                                                                                                                                                                              |

|        |                |          | 4. Connect ID0# to AMR PRIMARY_DN.                                                                                                                                                                                                                                                                        |

|        |                |          | 5. Leave ID1# open.                                                                                                                                                                                                                                                                                       |

|        |                |          | If PRIMARY_DN is low (codec is present on the motherboard), the ID is internally set to 01 for secondary codec operation and SDATA-IN1 is used. If PRIMARY_DN is high (codec is not present on the motherboard), the ID is internally set to set to 00 for primary codec operation and SDATA-IN0 is used. |

|        |                |          | For an MDC Board:                                                                                                                                                                                                                                                                                         |

|        |                |          | 1. Connect PRIMARY_DN to MDC PRIMARY_DN.                                                                                                                                                                                                                                                                  |

|        |                |          | 2. Connect SDATA_IN0 to SDATA_IN1.                                                                                                                                                                                                                                                                        |

|        |                |          | 3. Connect SDATA_IN0 or SDATA_IN1 to motherboard SDATA_IN through 33 $\Omega$ .                                                                                                                                                                                                                           |

|        |                |          | 4. Leave ID0# open.                                                                                                                                                                                                                                                                                       |

|        |                |          | 5. Leave ID1# open.                                                                                                                                                                                                                                                                                       |

|        |                |          | The MDC SDATA_INA signal should be used whether or not there is a primary codec.<br>PRIMARY_DN is high when audio codec is on the motherboard.                                                                                                                                                            |

|        |                |          | For a Modem-Only Mini PCI Board:                                                                                                                                                                                                                                                                          |

|        |                |          | 1. Connect PRIMARY_DN to GND.                                                                                                                                                                                                                                                                             |

|        |                |          | 2. Connect SDATA_IN0 to SDATA_IN1.                                                                                                                                                                                                                                                                        |

|        |                |          | 3. Connect SDATA_IN0 to SDATA_IN1 to motherboard SDATA_IN through 33 $\Omega$ .                                                                                                                                                                                                                           |

|        |                |          | 4. Connect ID0# to Mini PCI Codec_ID0#.                                                                                                                                                                                                                                                                   |

|        |                |          | 5. Connect ID1# to Mini PCI Codec_ID1#.                                                                                                                                                                                                                                                                   |

| SUBID0 | 27             | lt       | Sub Assembly ID 0. Connect to GND or +3.3V as defined by the OEM.                                                                                                                                                                                                                                         |

| SUBID1 | 28             | lt       | Sub Assembly ID 1. Connect to GND or +3.3V as defined by the OEM.                                                                                                                                                                                                                                         |

| SUBID2 | 45             | lt       | Sub Assembly ID 2. Connect to GND or +3.3V as defined by the OEM.                                                                                                                                                                                                                                         |

| SUBID3 | 46             | lt       | Sub Assembly ID 3. Connect to GND or +3.3V as defined by the OEM.                                                                                                                                                                                                                                         |

| RCOSC1 | 1              |          | <b>RC Circuit 1.</b> Connect to +3.3VDUAL/+3.3VSB through 249 KΩ 1%.                                                                                                                                                                                                                                      |

| GPIO4  | 47             | lt/Ot12  | General Purpose I/O. Reserved. If unused, connect to GND or +3.3V.                                                                                                                                                                                                                                        |

| GPIO5  | 48             |          |                                                                                                                                                                                                                                                                                                           |

| _                              |                  | Table                               | 3. HSD (11246) 48-pin TQFP Pin Signal Definitions (Cont'd)                                                                                                                                                                                                                                                                          |

|--------------------------------|------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Label                          | Pin              | I/O Type                            | Signal Name/Description                                                                                                                                                                                                                                                                                                             |

| PWRCLKP                        | 7                | Odpc                                | <b>Clock and Power Positive.</b> Provides clock and power to the LSD. Connect to the top of the DIB power and clock transformer (PCXFMR) primary winding.                                                                                                                                                                           |

| PWRCLKN                        | 8                | Odpc                                | <b>Clock and Power Negative.</b> Provides clock and power to the LSD. Connect to the bottom of the DIB power and clock transformer (PCXFMR) primary winding.                                                                                                                                                                        |

| DIB_DATAP                      | 4                | ldd/Odd                             | <b>Data Positive.</b> Transfers data, control, and status information between the HSD and LSD. Connect to the LSD through DIB data positive channel components.                                                                                                                                                                     |

| DIB_DATAN                      | 3                | Idd/Odd                             | <b>Data Negative.</b> Transfers data, control, and status information between the HSD and LSD.<br>Connect to the LSD through DIB data negative channel components.                                                                                                                                                                  |

|                                |                  |                                     | AC-link and AMR/MCD Interface                                                                                                                                                                                                                                                                                                       |

| BIT_CLK                        | 22               | lac/Oac                             | <b>Bit Clock</b> . 12.288 MHz serial data output bit clock derived from a 24.576 MHz external crystal circuit when the MC is configured as a primary codec. 12.288 MHz serial data input bit clock when the MC is configured as a secondary codec. Connect to AC97_BITCLK.                                                          |

| SYNC                           | 16               | lac                                 | <b>Frame Sync.</b> 48 kHz fixed rate sample AC-link sync input. Synchronization pulse from an AC'97 compliant controller to all of the AC'97 compliant codecs on the link. This signal is nominally 1.3 $\mu$ s wide pulse that is used to synchronize the AC-link. Reset state = low. Standard load = 50 pF. Connect to AC97_SYNC. |

| SDATA_OUT                      | 15               | lac                                 | <b>Serial Data Output.</b> Serial, time division multiplexed, input data stream from an AC'97 controller. Reset state = low. Standard load = 50 pF.                                                                                                                                                                                 |

|                                |                  |                                     | Connect to AC97_SDATA_OUT through 33 Ω.                                                                                                                                                                                                                                                                                             |

| SDATA_IN0                      | 21               | lac/Oac                             | Serial Data Input 0. Serial, time division multiplexed, input/output data stream.                                                                                                                                                                                                                                                   |

|                                |                  |                                     | Output data stream to an AC'97 controller when the SmartMC II is a Primary MC.                                                                                                                                                                                                                                                      |

|                                |                  |                                     | Input data stream from an AC'97 controller when the SmartMC II is a Secondary MC.                                                                                                                                                                                                                                                   |

|                                |                  |                                     | See ID0# and ID1# description in this table and Figure 6.                                                                                                                                                                                                                                                                           |

|                                | 20               | Oac                                 | Connect to AC97_SDATA_ IN0 through 33 $\Omega$ .                                                                                                                                                                                                                                                                                    |

| SDATA_IN1                      | 20               | Oac                                 | <b>Serial Data Input 1.</b> Serial, time division multiplexed, output data stream to an AC'97 controller when the SmartMC II is a Secondary MC.                                                                                                                                                                                     |

|                                |                  |                                     | See ID0# and ID1# description in this table and Figure 6.                                                                                                                                                                                                                                                                           |

|                                |                  |                                     | Connect to AC97_SDATA IN1 through 33 $\Omega$ .                                                                                                                                                                                                                                                                                     |

| AC_RESET#                      | 17               | lacl                                | AC '97 Master Hardware Reset. Active low reset. Reset state = low. Standard load = 50 pF.                                                                                                                                                                                                                                           |

| AO_RECEI#                      | 17               | laci                                | Connect to AC97_RESET.                                                                                                                                                                                                                                                                                                              |

| PRIMARY_DN                     | 14               | lt                                  | Primary Down. Used in conjunction with ID0# and ID1# to select modem codec operation as                                                                                                                                                                                                                                             |

|                                | 14               | n.                                  | a primary or secondary codec.                                                                                                                                                                                                                                                                                                       |

|                                |                  |                                     | See ID0# and ID1# description in this table and Figure 6.                                                                                                                                                                                                                                                                           |

| DSPKOUT                        | 13               | Ot12                                | Modem Speaker Digital Output. The DSPKOUT digital output reflects the received analog                                                                                                                                                                                                                                               |

|                                | 10               | 0112                                | input signal digitized to TTL high or low level by an internal comparator.                                                                                                                                                                                                                                                          |

|                                |                  |                                     | Connect to the MONO_PHONE signal through a filter circuit and optionally to an on-board speaker circuit, e.g., sounducer. The DSPKOUT output is used for call progress monitoring.                                                                                                                                                  |

|                                |                  | -                                   | Not Used                                                                                                                                                                                                                                                                                                                            |

| NC                             | 29-47            |                                     | No Connect. No internal connection.                                                                                                                                                                                                                                                                                                 |

| Notes:<br>1. I/O types:<br>lac | Digital input, a | AC-link-compatib                    | le, C <sub>IN</sub> = 50 pF (see Table 4)                                                                                                                                                                                                                                                                                           |

| lac/Oac                        |                  |                                     | le, C <sub>IN</sub> = 50 pF/Digital output, AC-link-compatible (see Table 4)                                                                                                                                                                                                                                                        |

| Idd/Odd                        |                  | it/DIB data outpu                   |                                                                                                                                                                                                                                                                                                                                     |

| lt                             | •                | TTL-compatible                      |                                                                                                                                                                                                                                                                                                                                     |

| lx                             | Crystal input    |                                     |                                                                                                                                                                                                                                                                                                                                     |

| Oac                            |                  |                                     | ible (see Table 4)                                                                                                                                                                                                                                                                                                                  |

| Odpc<br>Ot12                   |                  | nd clock output<br>, TTL-compatible | , 12 mA, $Z_{INTERNAL}$ = 32 $\Omega$                                                                                                                                                                                                                                                                                               |

| Ox<br>2. Interface Legend:     | Crystal input    | ,                                   |                                                                                                                                                                                                                                                                                                                                     |

| DIB                            | Digital Interfa  | ce Barrier                          |                                                                                                                                                                                                                                                                                                                                     |

| NC                             | No external c    | onnection                           |                                                                                                                                                                                                                                                                                                                                     |

| Table 3. HSD | (11246) 48 | nin TOFP Pin          | Signal D | efinitions ( | Cont'd) |

|--------------|------------|-----------------------|----------|--------------|---------|

|              | 11240740   | /=µiii i vagi i i iii | olgila D | cinna (i     | oont uj |

Figure 6. Modem Codec Primary/Secondary Codec Connections

| Parameter                                                                                                  | Symbol          | Min.  | Тур. | Max. | Units | Test Conditions |  |  |

|------------------------------------------------------------------------------------------------------------|-----------------|-------|------|------|-------|-----------------|--|--|

| Input Voltage                                                                                              | V <sub>IN</sub> | -0.30 | -    | 3.60 | VDC   | VDD = +3.6V     |  |  |

| Input Voltage Low                                                                                          | VIL             | _     | -    | 1.0  | VDC   |                 |  |  |

| Input Voltage High                                                                                         | VIH             | 1.6   | -    | -    | VDC   |                 |  |  |

| Output Voltage Low                                                                                         | V <sub>OL</sub> | 0     | -    | 0.33 | VDC   |                 |  |  |

| Output Voltage High                                                                                        | VOH             | 2.97  | -    | -    | VDC   |                 |  |  |

| Input Leakage Current (AC-link inputs)                                                                     | -               | -10   | _    | 10   | μA    |                 |  |  |

| Output Leakage Current (High-Z AC-link outputs)                                                            | -               | -10   | -    | 10   | μA    |                 |  |  |

| Notes:                                                                                                     |                 |       |      |      |       |                 |  |  |

| 1. Test Conditions unless otherwise stated: VDD = +3.3 ± 0.3 VDC; TA = 0°C to 70°C; external load = 50 pF. |                 |       |      |      |       |                 |  |  |

### Table 4. HSD (11246) Digital Electrical Characteristics - AC-link

|                 | Min.                                                  | Тур.                                                          | Max.                  | Units                                                  | Test Conditions                                        |

|-----------------|-------------------------------------------------------|---------------------------------------------------------------|-----------------------|--------------------------------------------------------|--------------------------------------------------------|

| V <sub>IL</sub> | -0.3                                                  | -                                                             | 0.8                   | VDC                                                    |                                                        |

| VIH             | 2.0                                                   | -                                                             | 3.6                   | VDC                                                    |                                                        |

| ۱ <sub>IL</sub> | -                                                     | -                                                             | -10                   | μA                                                     | $V_{IN} = 0$                                           |

| Iн              | -                                                     | -                                                             | +10                   | μA                                                     | V <sub>IN</sub> = +3.6V                                |

| ΊΗ              | _                                                     | _                                                             | +10                   | μΑ                                                     | _                                                      |

| 3 ± 0.3 VDC; TA | = 0°C to 7                                            | 0°C.                                                          |                       |                                                        |                                                        |

|                 | V <sub>IH</sub><br>I <sub>IL</sub><br>I <sub>IH</sub> | V <sub>IH</sub> 2.0<br>I <sub>IL</sub> –<br>I <sub>IH</sub> – | V <sub>IH</sub> 2.0 – | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

2. Current flow out of the device is shown as minus.

## AC Timing Characteristics

## AC Link Clocks

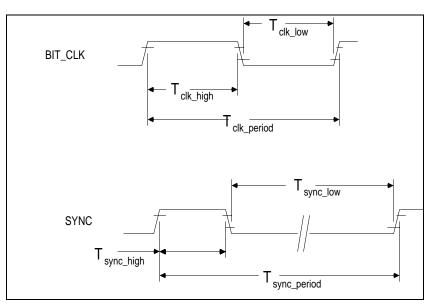

Figure 7. BIT\_CLK and SYNC Timing Waveforms

| Parameter                                          | Symbol                   | Min | Тур    | Max | Units |

|----------------------------------------------------|--------------------------|-----|--------|-----|-------|

| BIT_CLK frequency                                  |                          | -   | 12.288 | -   | MHz   |

| BIT_CLK period                                     | T <sub>clk_period</sub>  | -   | 81.4   | -   | ns    |

| BIT_CLK output jitter                              |                          | -   | -      | 750 | ps    |

| BIT_CLK high pulse width (note 2)                  | T <sub>clk_high</sub>    | 36  | 40.7   | 45  | ns    |

| BIT_CLK low pulse width (Note 2)                   | T <sub>clk_low</sub>     | 36  | 40.7   | 45  | ns    |

| SYNC frequency                                     |                          | -   | 48.0   | -   | kHz   |

| SYNC period                                        | T <sub>sync_period</sub> | -   | 20.8   | -   | μs    |

| SYNC high pulse width                              | T <sub>sync_high</sub>   | -   | 1.3    | -   | μs    |

| SYNC low pulse width                               | T <sub>sync_low</sub>    | -   | 19.5   | -   | μs    |

| Note 1: Worst case duty cycle restricted to 45/55. |                          |     |        |     |       |

| Note 2: 47.5-70 pF external load.                  |                          |     |        |     |       |

Table 6. BIT\_CLK and SYNC Timing Parameters

#### Data Output and Input

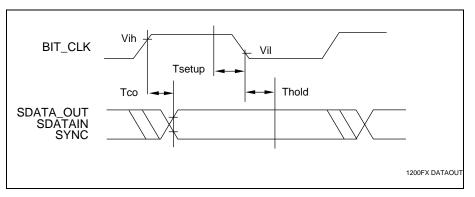

#### Figure 8. Data Output and Input Timing Waveforms

#### Table 7. AC-link Output Valid Delay Timing Parameters

| Parameter                                                                                              | Symbol | Min | Тур | Мах | Units |  |  |  |

|--------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-------|--|--|--|

| Output Valid Delay from rising edge of BIT_CLK                                                         | Тсо    | -   | -   | 15  | ns    |  |  |  |

| Note 1: Timing is for SDATA and SYNC outputs with respect to BIT_CLK at the device driving the output. |        |     |     |     |       |  |  |  |

| Note 2: 50 pF external load.                                                                           |        |     |     |     |       |  |  |  |

#### Table 8. AC-link Input Setup and Hold Timing Parameters

| Parameter                                                                                           | Symbol             | Min | Тур | Мах | Units |  |  |

|-----------------------------------------------------------------------------------------------------|--------------------|-----|-----|-----|-------|--|--|

| Input Setup to falling edge of BIT_CLK                                                              | T <sub>setup</sub> | 10  | -   | -   | ns    |  |  |

| Input Hold from falling edge of BIT_CLK                                                             | T <sub>hold</sub>  | 10  | -   | -   | ns    |  |  |

| Note: Timing is for SDATA and SYNC inputs with respect to BIT_CLK at the device latching the input. |                    |     |     |     |       |  |  |

#### Table 9. AC-link BIT\_CLK and SDATA Rise and Fall Time Timing Parameters

| Parameter                                                                                                     | Symbol | Min | Тур | Max | Units |  |

|---------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-------|--|

| BIT_CLK combined rise or fall plus flight time (Primary Codec to Controller or Secondary)                     |        | -   | -   | 7   | ns    |  |

| SDATA combined rise or fall plus flight time<br>(Output to Input)                                             |        | -   | -   | 7   | ns    |  |

| Note: Maximum combined rise or fall plus flight times are provided for worst case scenario modeling purposes. |        |     |     |     |       |  |

## Signal Rise and Fall Times

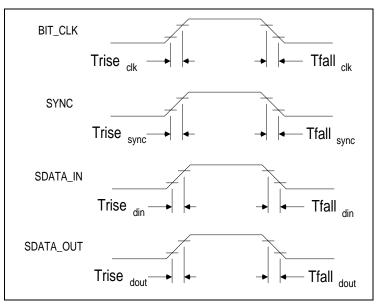

Figure 9. Signal Rise and Fall Time Timing Waveforms

| Table 10. Signal Rise and Fall Time Timing Parameters |  |

|-------------------------------------------------------|--|

|-------------------------------------------------------|--|

| Parameter                                        | Symbol                | Min | Тур | Max | Units |

|--------------------------------------------------|-----------------------|-----|-----|-----|-------|

| BIT_CLK rise time                                | Trise <sub>clk</sub>  | 2   | -   | 6   | ns    |

| BIT_CLK fall time                                | Tfall <sub>clk</sub>  | 2   | -   | 6   | ns    |

| SYNC rise time                                   | Trisesync             | 2   | -   | 6   | ns    |

| SYNC fall time                                   | Tfall <sub>sync</sub> | 2   | -   | 6   | ns    |

| SDATA_IN rise time                               | Trise <sub>din</sub>  | 2   | -   | 6   | ns    |

| SDATA_IN fall time                               | Tfall <sub>din</sub>  | 2   | -   | 6   | ns    |

| SDATA_OUT rise time                              | Trisedout             | 2   | -   | 6   | ns    |

| SDATA_OUT fall time                              | Tfall <sub>dout</sub> | 2   | -   | 6   | ns    |

| Note1: 50pF external load; from 10% to 90% of    | VDD.                  |     |     |     |       |

| Note 2: rise is from 10% to 90% of VDD (Vol to V | Voh).                 |     |     |     |       |

| Note 3: fall is from 90% to 10% of VDD (Voh to V | Vol).                 |     |     |     |       |

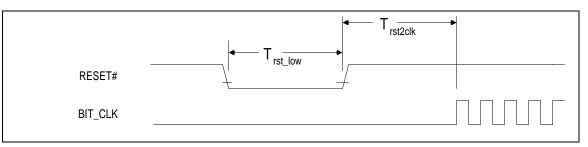

## RESET# (Cold Reset)

Figure 10. Cold Reset Timing Waveforms

| T-11- 44  | 0.1.1 | D 4   | Therefore | D          |

|-----------|-------|-------|-----------|------------|

| Table 11. | Cola  | Reset | iiming    | Parameters |

| Parameter                                | Symbol               | Min   | Тур | Мах | Units |

|------------------------------------------|----------------------|-------|-----|-----|-------|

| RESET# active low pulse width            | T <sub>rst_low</sub> | 1.0   | -   | -   | μs    |

| RESET# inactive to BIT_CLK startup delay | T <sub>rst2clk</sub> | 162.8 | -   | -   | ns    |

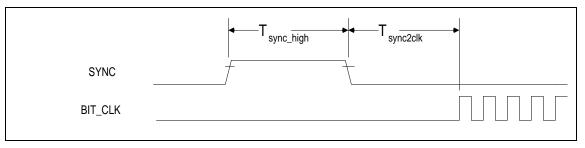

## RESET# (Warm Reset)

### Figure 11. Warm Reset Timing Waveforms

#### Table 12. Warm Reset Timing Parameters

| Parameter                                                                                                                                              | Symbol                 | Min   | Тур | Мах | Units |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|-----|-----|-------|--|--|--|--|--|--|

| SYNC active high pulse width                                                                                                                           | T <sub>sync_high</sub> | 1.0   | -   | -   | μs    |  |  |  |  |  |  |

| SYNC inactive to BIT_CLK startup delay                                                                                                                 | T <sub>sync2clk</sub>  | 162.8 | -   | -   | ns    |  |  |  |  |  |  |

| Note: The minimum SYNC pulse width pertains to warm reset only, during normal operation, SYNC is asserted for the entire tag phase (16 BIT_CLK times). |                        |       |     |     |       |  |  |  |  |  |  |

#### AC-link Low Power Mode Timing

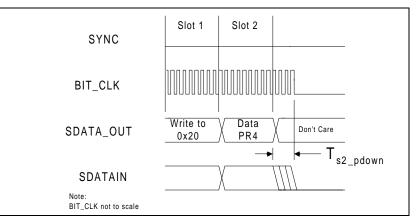

Figure 12. AC-link Low Power Mode Timing Waveforms

| Table 13. AC-link Low Power Mode | Timing Parameters |

|----------------------------------|-------------------|

|----------------------------------|-------------------|

| Parameter                              | Symbol                | Min | Тур | Мах | Units |

|----------------------------------------|-----------------------|-----|-----|-----|-------|

| End of Slot 2 to BIT_CLK, SDATA_IN low | T <sub>s2_pdown</sub> | -   | -   | 1.0 | μs    |

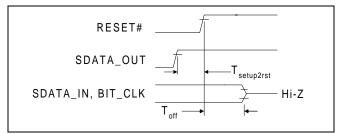

#### ATE Test Mode Timing

Figure 13. ATE Test Mode Timing Waveforms

| Parameter                                               | Symbol                 | Min  | Тур | Мах  | Units |

|---------------------------------------------------------|------------------------|------|-----|------|-------|

| Setup to trailing edge of RESET# (also applies to SYNC) | T <sub>setup2rst</sub> | 15.0 | -   | -    | ns    |

| Rising edge of RESET# to Hi-Z delay                     | T <sub>off</sub>       | -    | -   | 25.0 | ns    |

#### AC-link IO Pin Capacitance and Loading

In multiple Codec implementations, the AC '97 2.1 Controller can drive SYNC and SDATA\_OUT to two or more destinations. The Controller's SYNC and SDATA\_OUT output pin drivers must meet AC-link timing requirements when loaded by the total capacitance on each of these outputs.

In multiple Codec implementations, the SmartMC II can drive BIT\_CLK to 1 or 2 destinations. The Codec's BIT\_CLK output pin driver meets AC-link timing requirements when loaded by the total capacitance on this output.

The following factors contribute to total capacitance:

- Controller or Codec output pin capacitance (internal device characteristic)

- Codec or Controller input pin capacitance (7.5 pF max per AC '97 2.1, see Table 15)

- Total trace length capacitance on motherboard plus riser (estimated 2.5 pF per inch). Note that motherboard plus riser trace lengths, especially in multiple Codec implementations such as AC down (motherboard) and MC up (riser), could exceed ~15 inches, particularly in NLX form factor designs.

- IO connectors, such as motherboard to riser (estimated 2.5 pF)

AC '97 2.1 compatibility recommends that the following Controller and Codec input pins have a maximum of 7.5 pF capacitance:

- Controller BIT\_CLK and SDATA\_IN[0-3] inputs

- Primary and Secondary Codec SYNC and SDATA\_OUT inputs

- Secondary Codec BIT\_CLK input

AC '97 2.1 compatibility recommends the Controller and Codec AC-link output pin drivers identified in Table 15 be of sufficient strength to meet AC-link timing requirements for the following specified external capacitive loads in 1-4 Codec implementations. In addition to these external capacitive loads, additional allowance must be made for the particular Controller or Codec output pin capacitance (internal device characteristic).

| Output pin                                                                     | Capacitance:<br>1 Codec | Capacitance:<br>2 Codecs                                                      |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Controller: SYNC, SDATA_OUT                                                    | 47.5 pF                 | 55 pF                                                                         |  |  |  |  |  |  |  |  |  |

| Codec: BIT_CLK (can support 2 codecs)                                          | 55 pF                   | 55 pF                                                                         |  |  |  |  |  |  |  |  |  |

| Codec: SDATA_IN (point to point)                                               | 47.5 pF                 | 47.5 pF                                                                       |  |  |  |  |  |  |  |  |  |

| Notes:                                                                         |                         |                                                                               |  |  |  |  |  |  |  |  |  |

| 47.5 pF load comprehends 1 input, 1 connector, and ~15 inches of trace length. |                         |                                                                               |  |  |  |  |  |  |  |  |  |

| 55 pF load comprehends 2 inputs, 1 connector, and                              | ~15 inches of trace ler | 55 pF load comprehends 2 inputs, 1 connector, and ~15 inches of trace length. |  |  |  |  |  |  |  |  |  |