**ATM on Fractional E1/T1**

AF-PHY-0130.00

October, 1999

© 1999 by The ATM Forum. This specification/document may be reproduced and distributed in whole, but (except as provided in the next sentence) not in part, for internal and informational use only and not for commercial distribution. Notwithstanding the foregoing sentence, any protocol implementation conformance statements (PICS) or implementation conformance statements (ICS) contained in this specification/document may be separately reproduced and distributed provided that it is reproduced and distributed in whole, but not in part, for uses other than commercial distribution. All other rights reserved. Except as expressly stated in this notice, no part of this specification/document may be reproduced or transmitted in any form or by any means, or stored in any information storage and retrieval system, without the prior written permission of The ATM Forum.

The information in this publication is believed to be accurate as of its publication date. Such information is subject to change without notice and The ATM Forum is not responsible for any errors. The ATM Forum does not assume any responsibility to update or correct any information in this publication. Notwithstanding anything to the contrary, neither The ATM Forum nor the publisher make any representation or warranty, expressed or implied, concerning the completeness, accuracy, or applicability of any information contained in this publication. No liability of any kind shall be assumed by The ATM Forum or the publisher as a result of reliance upon any information contained in this publication.

The receipt or any use of this document or its contents does not in any way create by implication or otherwise:

- Any express or implied license or right to or under any ATM Forum member company's patent, copyright, trademark or trade secret rights which are or may be associated with the ideas, techniques, concepts or expressions contained herein; nor

- Any warranty or representation that any ATM Forum member companies will announce any product(s) and/or service(s) related thereto, or if such announcements are made, that such announced product(s) and/or service(s) embody any or all of the ideas, technologies, or concepts contained herein; nor

- Any form of relationship between any ATM Forum member companies and the recipient or user of this

document.

Implementation or use of specific ATM standards or recommendations and ATM Forum specifications will be voluntary, and no company shall agree or be obliged to implement them by virtue of participation in The ATM Forum.

The ATM Forum is a non-profit international organization accelerating industry cooperation on ATM technology. The ATM Forum does not, expressly or otherwise, endorse or promote any specific products or services.

NOTE: The user's attention is called to the possibility that implementation of the ATM interoperability specification contained herein may require use of an invention covered by patent rights held by ATM Forum Member companies or others. By publication of this ATM interoperability specification, no position is taken by The ATM Forum with respect to validity of any patent claims or of any patent rights related thereto or the ability to obtain the license to use such rights. ATM Forum Member companies agree to grant licenses under the relevant patents they own on reasonable and nondiscriminatory terms and conditions to applicants desiring to obtain such a license. For additional information contact:

The ATM Forum Worldwide Headquarters 2570 West El Camino Real, Suite 304 Mountain View, CA 94040-1313 Tel: +1-650-949-6700

Fax:+1-650-949-6705

#### 1. Introduction.

This document specifies the requirements for the ATM Forum on how to map ATM on a "circuit-mode connection" supporting unrestricted information transfer rates at integer multiples of 64 kbit/s up to the maximum rate of the interface (ref: ITU-T rec. I.231.10 [1]). The physical interface may typically be DS1 or E1 (or any other physical interface). The specification shall apply for any N\*64 kbit/s rate up to 1920 kbit/s (N=30) and be independent of type of interface (UNI or NNI).

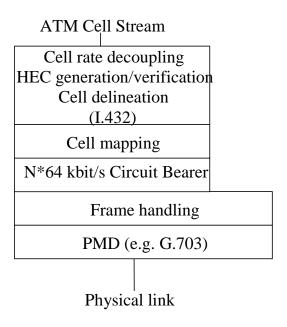

Figure 1 shows the physical layer functionality of ATM when mapped on a circuit bearer.

Figure 1 Physical Layer Functions for transfer rates at integer multiples of 64 kbit/s.

Observe that the mechanism for how to map ATM on a circuit bearer is not different from the general mechanism described in earlier specifications, e.g. in af-phy-0064.000 [2], "E1 Physical Interface Specification" and in G.804, [3] "ATM Cell Mapping into Plesiochronous Digital Hierarchy".

#### 2. Acronyms

| HEC   | Header Error Control                                      |

|-------|-----------------------------------------------------------|

| ISDN  | Integrated Services Digital Network                       |

| ITU-T | International Telecommunication Union - Telecommunication |

| NNI   | Network-Node Interface                                    |

| PMD   | Physical Medium Dependent                                 |

| TC    | Transmission Convergence                                  |

UNI User Network Interface

# 3. Physical Medium Dependent (PMD) Sublayer

Will not be defined in this specification.

The content of this specification is independent of the PMD sublayer.

## 4. N\*64 kbit/s Circuit Sublayer

# 4.1 Transport Specific TC Functions

### 4.1.1 N\*64 kbit/s Circuit Bearer Transmission Frame Format

The N\*64 kbit/s circuit bearer transmission frame format specified here is compliant to the ISDN "Circuit-mode Multiple-rate Unrestricted 8 kHz Structured Bearer Service Category (ref: ITU-T rec. I.231.10 [1]). The N\*64 kbit/s circuit bearer for ATM allows only point-to-point configurations.

- **(R1)** The assignment of the N 64 kbit/s time slots shall support both contiguous and non-contiguous configuration. The assignment has only local meaning. In particular, the contiguous assignment at one interface does not mean that the time slots are assigned contiguously within the network or at the terminating interface.

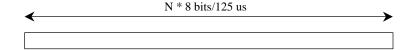

- (**R2**) The N\*64 kbit/s Circuit Bearer shall support octet alignment of an unrestricted octet stream supporting sequence integrity. The transmission frame shall consist of N time slots (octets). The frame repetition rate is 8000 Hz. All timeslots of the N\*64 kbit/s Circuit Bearer shall be available for carrying data traffic. The frame is shown in Figure 2.

Figure 2 N\*64 kbit/s Circuit Bearer Frame Structure

- (R3) The N\*64 kbit/s time slots selected shall belong to a single physical interface

- **(R4)** The number of assigned time slots is symmetrical.

- (R5) The N\*64 kbit/s circuit bearer shall support assignment of all those time slots, which are meant for user data traffic in the physical interface specifications. (E.g. TS0 and TS16 at the E1 interface are by default reserved and not available for circuit bearer)

# **4.1.2** Frame Handling

**(R6)** Framing shall be provided by the physical layer as a primitive.

# **4.2 ATM-Specific TC Functions**

# 4.2.1 ATM Cell Mapping

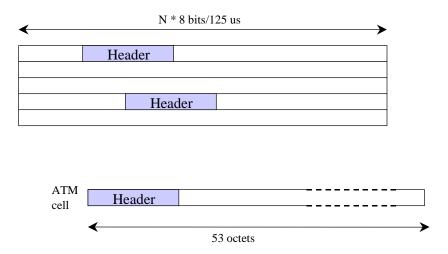

(R7) The ATM cell is mapped into all bits of the N\*64 kbit/s Circuit Bearer frame as shown in Figure 3. The ATM cell octet structure shall be aligned with the octet structure of the frame.

(**R8**) There shall be no relationship between the beginning of an ATM cell and the beginning of an N\*64 kbit/s Circuit Bearer frame.

Note: Since the frame payload capacity (N octets) is not an integer multiple of cell length (53 octets), ATM cells will cross the N\*64 kbit/s Circuit Bearer frame boundary.

Figure 3 N\*64 kbit/s Circuit Bearer Frame Structure Used to Transport ATM Cells.

## 4.2.2 Cell Rate Decoupling

**(R9)** The cell rate adaptation to the payload capacity of the N\*64 kbit/s Circuit Bearer frame (N\*64 kbit/s) shall be performed by the insertion of idle cells as defined in ITU-T Recommendation I.432.1 [4], Section 7.3.5. The header (and payload) pattern for idle cells shall be as defined in [4], Table3/I.432.1.

# 4.2.3 Header Error Control (HEC) Processing

(R10) The Header Error Control (HEC) value shall be verified as specified by ITU-T Recommendation I.432.1 [4], Section 7.3.2.1.

- (O1) When single bit HEC errors are corrected, this shall be done as specified by ITU-T Recommendation I.432.1 [4], Section 7.3.2.1.

- (R11) The Header Error Control (HEC) value shall be generated in compliance with ITU-T Recommendation I.432.1 [4], Section 7.3.2.2.

# 4.2.4 Cell Delineation and Scrambling

- (R12) The cell delineation function shall be performed using the HEC mechanism as defined in ITU-T Recommendation I.432.1 [4], Section 7.3.3.

- (R13) The ATM cell payload shall be scrambled using a self-synchronizing scrambler with polynomial  $x^{43}$  + 1as defined in ITU-T Recommendation I.432.1 [4], Section 7.3.4.1.

### 5. References

- [1] ITU-T Recommendation I.231.10 on "Circuit-mode Multiple-rate Unrestricted 8 kHz Structured Bearer Service Category", August 1992.

- [2] ATM Forum af-phy-0064.000, E1 Physical Interface Specification, September 1996.

- [3] ITU-T Recommendation G.804, ATM Cell Mapping into Plesiochronous Digital Hierarchy (PDH), July 1995.

- [4] ITU-T Recommendation I.432.1 on B-ISDN user-network interface Physical layer specification: General characteristics, February 1999.